我国科学家开发首个二维-硅基混合架构芯片

手握“长缨”,他们开发首个二维-硅基混合架构芯片

4月16日,复旦大学教授周鹏、研究员刘春森团队的研究论文在《自然》上线。团队研制的“破晓(PoX)”二维闪存原型器件,颠覆现有闪存技术路径,实现了400皮秒超高速非易失存储,是迄今最快的半导体电荷存储技术。

开心的同时,刘春森又去查阅了下《自然》编辑部的邮件。“您的稿件已被三位审稿人评阅,他们均认为这项工作具有潜在研究价值,我们对此表示赞同。”

这是团队同步开展的另一项工作。他们提出了二维-硅基混合架构“长缨(CY-01)”,通过将二维闪存器件直接融入成熟的互补金属氧化物半导体(CMOS)工艺平台,加快这种新型器件的产业化。

周鹏(前排右三)、刘春森(前排右四)团队。

10月8日,这项让刘春森牵挂着的研究在《自然》以“加速上线”的形式发表,刘春森是第一作者兼通讯作者,周鹏为通讯作者。《自然》同行评议“有望引起商业公司高度关注”。

“从0到10”,面向未来

毫无疑问,存储器目前是一个非常成熟的产业,人们早已习惯了易失性存储和非易失性存储两套系统共同工作的模式——前者以SRAM、DRAM为代表,操作速度快,但容量小,数据在断电后无法保存;后者以闪存为代表,容量大,无需电源即可保存数据,但运行速度较慢。

“过去几十年间,国际上提出了多种新型存储技术路径,但始终没有颠覆现有存储芯片格局。”刘春森坦言,“以闪存为例,它的结构十分简单,而且运行稳定性高、价格便宜,在以上方面难以被取代。”

突破现有存储技术瓶颈困难重重,却并未让周鹏和刘春森等科学家退缩,他们始终致力于开发能够满足未来人工智能(AI)应用的颠覆性存储技术。

刘春森解释:“AI大模型对数据存储有了读取速度快和高容量兼顾的要求,现有存储器均无法满足此需求。可以说,存储器是制约AI发展主要的硬件瓶颈之一。”

过去十年间,周鹏、刘春森团队聚焦二维超快闪存技术,从“0”起步,从底层物理原理出发,一步步往前迈进。2018年他们报道了首个高速准非易失闪存,2021年进一步发现了辅助势垒隧穿增强机理,将读写速度提至20纳秒的同时,确保了数据存储的非易失性。以上进展让他们意识到二维闪存器件有产业化的价值,开始同步开展器件集成方面的工作。

“二维超快闪存技术是我们团队自主提出、国际上独一无二的技术路线,读写速度远超现有闪存技术。”刘春森说道,“事实上,我们一直在深入研究二维高速存储器件,在研究过程中,逐渐建立起向下游应用推进的信心。”

“从10到0”,借道加速

新型器件要真正走向系统级应用,往往是一场漫长的马拉松。以集成电路发展为例,半导体晶体管诞生于1947年,之后历经贝尔实验室和一系列顶尖公司接力研发,才在24年后催生出全球第一颗CPU。

而对于一个专于器件研发的团队,从基础研究到产业应用的“转型”,更是不易。“颠覆性创新走向工程化应用,本质上是一条从‘0到10’的征途。而要真正走通这条路,离不开从‘10到0’,即从未来应用的终点出发,倒推技术发展的正确路径。”周鹏表示。

顺着这个思路,团队意识到,二维闪存无需再走长达几十年的研发之路,完全可以“站在巨人的肩膀上”,缩短技术落地进程。

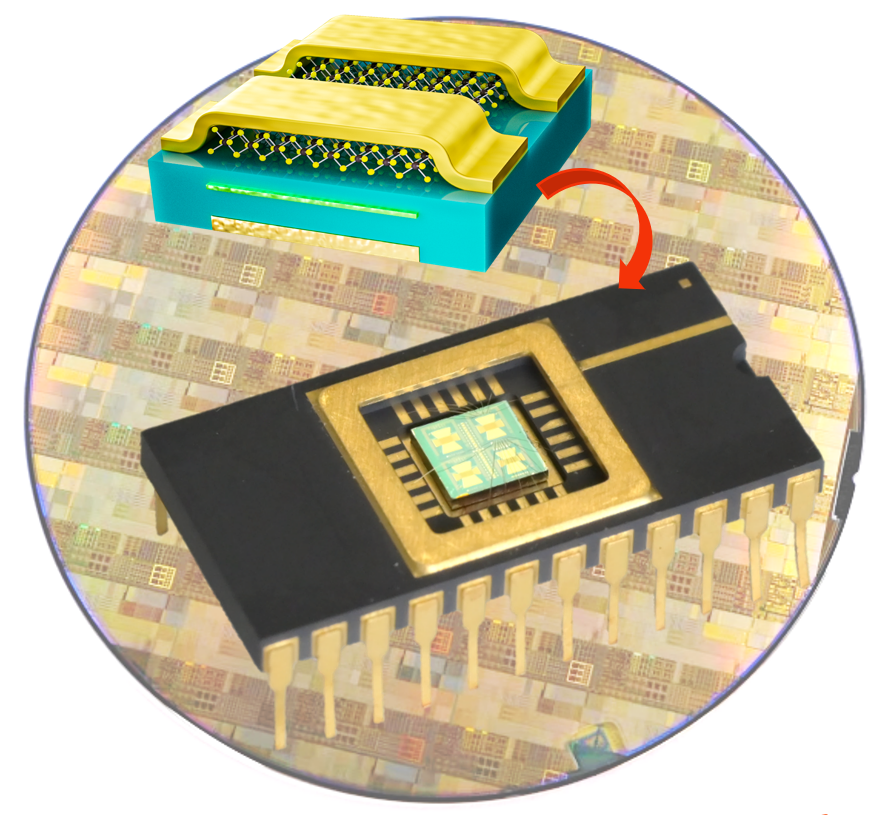

何不借助现有成熟硅基CMOS制造工艺这条“高速公路”,让二维存储器件这一新型“交通工具”行驶得更快呢?由此,团队基于“长缨”架构,攻克了新型二维信息器件工程化的关键难题,制备得到全球首颗二维-硅基混合架构芯片。测试结果显示,该新型存储芯片的集成良率达94.3%,支持8比特指令操作,32比特高速并行操作与随机寻址。

世界首颗二维-硅基混合架构闪存芯片。图片均由复旦大学提供

期间,他们主要攻克了两大瓶颈问题。

一方面,传统CMOS制造工艺与厚度达数百微米、具备金刚石结构的硅材料相适配,而二维材料厚度仅为1-3个原子,直接使用此工艺无疑会引入“材料暗伤”。

团队针对性地研发了“原子芯片(ATOM2CHIP)”系统集成框架。就像拼乐高积木一样,他们通过模块化集成方案,将二维存储电路与成熟CMOS电路分离制造,最后与CMOS控制电路通过高密度单片互连技术实现完整芯片集成。

“这一集成框架的核心思路,是在时空上分割二维存储电路和CMOS电路的制造。”刘春森解释道,“我们首先采用标准CMOS工艺制造CMOS控制电路,再利用支持原子尺度贴合的片上二维集成工艺进行二维电路的后续工艺集成,由此确保制造流程受到最小化的影响。”

另一方面,二维存储器件的工作机制与标准CMOS不兼容。针对此问题,团队提出了跨平台系统设计方法论,在二维存储电路和CMOS电路之间专门添加了“转译层”,并结合高密度单片互连技术,实现了二维电路和CMOS电路软、硬件兼容性通信。

刘春森说道:“由此,CMOS电路能够理解二维器件的工作模式,二维电路也能够理解从CMOS电路传递过来的控制信号。”

“从10到100”,拥抱产业

这项成果突破,也离不开周鹏、刘春森团队和工业界的深度合作。在项目开展之初,他们就决定只做自己擅长的事情,专注于二维存储器件部分,而芯片整体设计、控制和读出电路等则交由合作企业完成。

目前,团队正在着手建设中试线,预计在未来3至5年内将芯片容量从Kb扩展到Mb级别。“在5至10年的视角,我们计划进一步与企业合作,利用产业界成熟的工艺和大规模产线,将存储容量做到Gb甚至Tb,实现第一批商业化产品落地。”刘春森表示。

届时,当前分级存储架构将被改变,一块存储芯片即可同时实现高读写速率、大容量及数据长期保存,有望将AI服务器部署在个人电脑甚至手机上,进一步推动AI应用和发展。此外,以垂直堆叠为特点的3D NAND闪存芯片制备工艺也有可能实现新的颠覆性突破。

“以长缨为架构、破晓为内核的二维芯片是二维电子器件工程化里程碑,也为新一代颠覆性器件缩短应用化周期提供了范例。”周鹏自信地表示。

相关论文信息:http://doi.org/10.1038/s41586-025-09621-8

| 分享1 |

| 相关资讯 |

| 图片资讯 | 更多 |

| 一周资讯排行 | 更多 |

关于我们 | 网站声明 | 服务条款 | 联系方式

京ICP备 14047472号-1

京公网安备 11010502030844号

京公网安备 11010502030844号